# SPICE Modeling and CMOS Circuit Development of a SiC Power IC Technology

Tianshi Liu\*, Hua Zhang\*, Sundar Babu Isukapati<sup>†</sup>, Emaran Ashik<sup>§</sup>, Adam J. Morgan<sup>†</sup>,

Bongmook Lee<sup>§</sup>, *Senior Member, IEEE*, Woongje Sung<sup>†</sup>, *Member, IEEE*, Marvin H. White\*, *Life Fellow, IEEE*,

Ayman Fayed\*, *Senior Member, IEEE*, and Anant K. Agarwal\*, *Fellow, IEEE*\*Dept. of Electrical & Computer Eng., The Ohio State University, Columbus, Ohio, USA

<sup>†</sup>College of Nanoscale Sci. and Eng., State University of New York Polytechnic Institute, Albany, NY, USA.

<sup>§</sup>Dept. of Electrical. & Computer Eng., North Carolina State University, Raleigh, NC, USA.

Abstract—This paper presents the SPICE modeling and circuit development of a SiC power integrated circuit (IC) technology that offers monolithic integration of high-voltage lateral ntype SiC power metal-oxide-semiconductor field-effect transistors (MOSFETs) and low-voltage SiC complementary-MOS (CMOS) devices. The SPICE models are based on two-dimensional device simulations with the Sentaurus TCAD device simulator. With the developed SPICE models, this technology enables the design of application specific integrated circuits (ASICs) in SiC, such as fully integrated high-voltage SiC power converters, that can work in high temperature and radioactive environments. Circuit simulations of a SiC CMOS inverter and a SiC ring oscillator are included to demonstrate the technology.

*Index Terms*—SiC ICs, CMOS design in SiC, Power ICs, SPICE modeling.

# I. Introduction

Currently, the main focus of the silicon carbide (SiC) technology is on discrete power devices, such as SiC vertical power MOSFETs, because the larger bandgap and higher breakdown electric field of SiC allow superior SiC-based power electronics compared to their silicon (Si) counterparts [1], [2]. These inherent material properties also make SiC integrated circuits (ICs) attractive in specific applications, such as subterranean and interplanetary explorations and high-temperature data acquisition [3], where the electronics operate under harsh environments. Therefore, SiC ICs have also gained attention.

SiC IC research began in the 1990s, where the early studies were conducted on both 6H-SiC and 4H-SiC wafers with low-voltage (LV) all n-type MOSFET (NMOS) processes [4]–[6]. With material and process improvement, Raytheon Systems Limited (RSL) developed a 1.2-μm 4H-SiC complementary metal–oxide–semiconductor (CMOS) process (HiTSiC). A process design kit (PDK) was also developed for this process [7]. Since then, various LV SiC CMOS circuits have been demonstrated with the HiTSiC process and its PDK [3], [8]–[13]. Recently, Barlow et al. reported a SiC CMOS gate driver that can drive CREE 3rd generation SiC power MOSFETs at over 500°C [3].

The information, data, or work presented herein is funded by Advanced Research Projects Agency-Energy (ARPA-E) U.S. Department of Energy, under Award Number DE—AR0001028.

SiC bipolar junction transistors (BJTs) and SiC junction field-effect-transistors (JFETs) based ICs have also been developed for extreme-temperature operations. Hou et al. reported a 16x16 SiC BJT-based UV image sensor array operational at 400°C [14]. Neudeck et al. [15] have also demonstrated SiC JFET-based digital ICs that operate across a wide range of temperature span (-190°C to 812°C).

Previous SiC IC efforts focused on low-voltage applications. This work presents a SiC power IC technology that offers monolithic integration of high-voltage (HV) lateral SiC power MOSFETs and low voltage SiC CMOS devices. The proposed technology enables application specific integrated circuits (ASICs) in SiC, such as fully integrated SiC power converters to operate at elevated temperatures with higher power ratings. Level 2 SPICE models are developed based on two-dimensional (2-D) TCAD simulations for both the LV CMOS and HV NMOS devices. Simulations of a SiC CMOS inverter and a SiC ring-oscillator are demonstrated with the developed SPICE models.

# II. 2-D TCAD SIMULATION

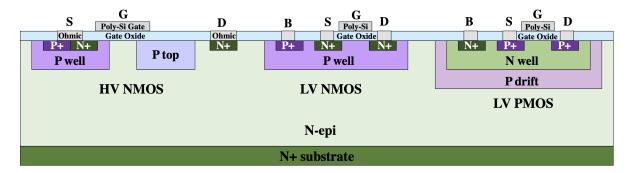

Fig. 1 shows the cross-sectional views of the SiC HV NMOS, LV NMOS, and LV PMOS. All MOSFETs are designed with the Sentaurus TCAD device simulator, and the simulations are based on an actual fabrication process in collaboration with the team at the ADI Hillview facility. The N-type drift layer is 6  $\mu m$  thick and with  $2.5 \times 10^{16} cm^{-3}$  doping concentration. The

TABLE I

TCAD SIMULATIONS FOR SPICE PARAMETER EXTRACTIONS

| I-V simulaitons | Simulation conditions           | SPICE parameters      |

|-----------------|---------------------------------|-----------------------|

| Ids vs. Vgs     | Vds=0.1 V                       | VTO, GAMMA,           |

|                 | Vgs= $0\sim25$ V, step= $50$ mV | NSUB, PHI,            |

|                 | Vbs=0 $\sim$ -6 V, step=-1 V    | UO, UEXP, UCRIT       |

| Ids vs. Vds     | Vbs=0 V                         | LAMBDA, VMAX,<br>NEFF |

|                 | Vds= $0\sim25$ V, step= $0.5$ V |                       |

|                 | Vgs= $0\sim25$ V, step= $5$ V   |                       |

Fig. 1. Cross-sectional views of the HV NMOS, LV NMOS, and LV PMOS on the N-epi/N+ substrate are shown.

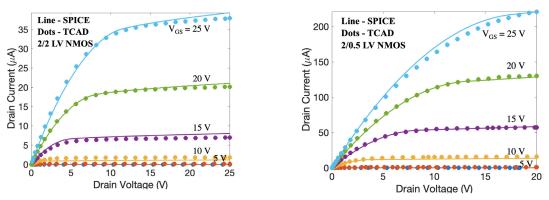

Fig. 2. TCAD-simulated (dots) and SPICE-simulated (solid lines) output characteristics of a 2 \(\mu m/2\) \(\mu m\) (left) and 2 \(\mu m/0.5\) \(\mu m\) (right) SiC LV NMOS.

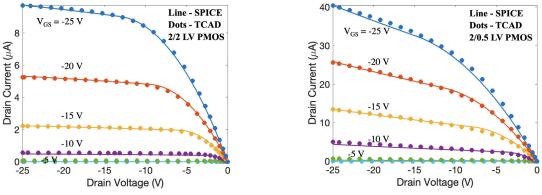

Fig. 3. TCAD-simulated (dots) and SPICE-simulated (solid lines) output characteristics of a 2  $\mu m/2$   $\mu m$  (left) and 2  $\mu m/0.5$   $\mu m$  (right) SiC LV PMOS.

gate oxide thicknesses are 50 nm for all MOSFETs. The single Reduced Surface Field (RESURF) technique [16] is utilized for the HV NMOS to manage the surface electric field and have a blocking voltage of over 600 V.

The expected electron and hole mobilities are  $20\,\mathrm{cm^2\,V^{-1}\,s}$  and  $5\,\mathrm{cm^2\,V^{-1}\,s}$ , respectively. The well doping concentrations of the LV NMOS and LV PMOS are adjusted so that the threshold voltages are around 6 V for both types of LV MOSFETs. The maximum supply voltage is set at  $25\,\mathrm{V}$ . More comprehensive details regarding the device design and fabrication are included in [17]. Different types of 2-D simulations (shown in Table. I) are conducted to provide the necessary results for SPICE parameter extractions and model development (discussed in the next section).

## III. SPICE MODELING

This section introduces the level 2 SPICE model and demonstrates the static performances of the developed level 2 SPICE models for the LV NMOS, LV PMOS, and HV NMOS. The level 2 SPICE model is a physics-based model with empirical parameters for improving the simulation accuracy. It is based on the Shichman-Hodges model (level 1) with added secondary effects such as carrier velocity saturation and mobility dependence of the vertical electric field [18].

The threshold voltage at zero body bias (VTO), the bulk threshold parameter (GAMMA), the substrate doping (NSUB), and the surface potential (PHI) are extracted from an iterative process with Ids vs. Vgs results under different substrate biases [19]. The mobility-related parameters (UO, UEXP, and UCRIT)

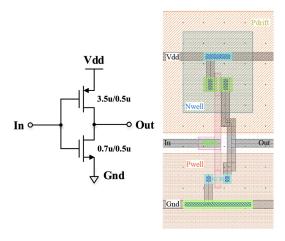

Fig. 4. Schematic (left) and layout (right) of the SiC CMOS inverter.

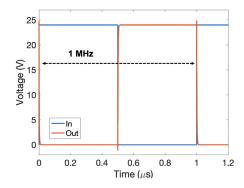

Fig. 5. Dynamic simulation of the SiC CMOS inverter with a 1 MHz input.

are extracted from the same data set. The channel length modulation (LAMBDA), carrier saturation velocity (VMAX), and depletion charge reduction parameter (NEFF) are extracted from the Ids vs. Vds simulations. Level 2 SPICE models are constructed based on the extracted parameters. Comparison between the SPICE simulations and TCAD simulations for selected NMOS and PMOS are presented in Fig. 2 and Fig. 3, respectively. High accuracy of the SPICE models is achieved for all types of MOSFETs. The developed SPICE models are incorporated into Cadence Virtuoso Analog Design Environment (ADE) for circuit simulations.

# IV. CIRCUIT DEVELOPMENT AND SIMULATION

In this section, the SPICE simulations of a SiC CMOS inverter and a SiC ring oscillator are presented to demonstrate the proposed technology. The design considerations, simulation results, and the corresponding layouts of the two types of circuits are discussed.

# A. SiC CMOS Inverter

Fig. 4 shows the schematic and layout design of a SiC CMOS inverter. Minimum channel length  $(0.5~\mu m)$  is applied to both transistors and the minimum channel width  $(0.7~\mu m)$  is used

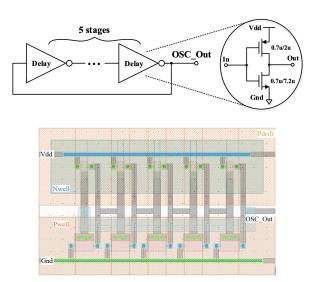

Fig. 6. Schematic (top) and layout (bottom) of the the 5-stage SiC ring oscillator.

for the LV NMOS to optimize the delay time. The width of the LV PMOS is sized to be five times the width of the LV NMOS to have identical rise time and fall time. This ratio is determined by the expected electron mobility  $(20\,\mathrm{cm^2\,V^{-1}\,s^{-1}})$  and hole mobility  $(4\,\mathrm{cm^2\,V^{-1}\,s^{-1}})$  in the channel. The inverter is simulated with a  $V_{\rm dd}$  of 24 V and an input square signal of 1MHz, and the transient simulation result is shown in Fig. 5. The simulated rise and fall time is  $3.2\,\mathrm{ns}$ .

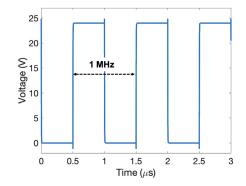

Fig. 7. Dynamic simulation of the SiC ring oscillator.

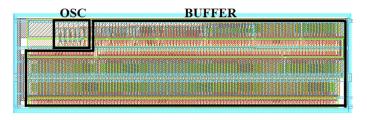

Fig. 8. Complete layout of the SiC ring oscillator with the buffer stage.

### B. SiC Ring Oscillator

A ring oscillator is usually implemented to generate the on-chip clock signal. Fig. 6 shows the schematic and layout designs of a 1MHz SiC ring oscillator. The LVNMOS and LPMOS in each delay cell are sized as  $0.7\mu m/7.2\mu m$  and  $0.7\mu m/7.2\mu m$  to achieve  $100\,\mathrm{ns}$  delay time and the identical rise/fall time. The ring oscillator is simulated with a  $V_{\mathrm{dd}}$  of 24V, and the output signal is demonstrated in Fig. 7, showing a 1MHz oscillating frequency. To drive the parasitic capacitance of probing pads ( $\sim 100\mathrm{pF}$ ), a buffer, which is a tapered inverter chain, is cascaded with the oscillator. The layout of the buffered oscillator is shown in Fig. 8.

The inverter and oscillator designs are sent out for fabrication. Characterizations of the fabricated circuits will be reported in future publications.

#### V. SUMMARY

Level 2 SPICE models are developed for a SiC power IC technology that offers monolithic integration between high-voltage SiC power MOSFETs and low voltage SiC CMOS devices. Based on 2-D device simulations, accurate fittings are achieved for the developed SPICE models of the low-voltage NMOS and PMOS with different channel lengths. The models are integrated into Cadence Virtuoso Analog Design Environment for circuit simulations. Dynamic simulations and layout designs of a SiC CMOS inverter and a SiC ring oscillator are presented. The authors have sent out the inverter and the oscillators for fabrication.

## ACKNOWLEDGMENTS

The work presented herein is funded by Advanced Research Projects Agency-Energy (ARPA-E) U.S. Department of Energy, under Award Number DE—AR0001028. The authors would also like to thank the team at ADI Hillview facility for the helpful discussions.

# REFERENCES

- M. Yamamoto, T. Kakisaka, and J. Imaoka, "Technical trend of power electronics systems for automotive applications," *Japanese Journal of Applied Physics*, vol. 59, no. SG, p. SG0805, 2020.

- [2] T. Kimoto, "Material science and device physics in sic technology for high-voltage power devices," *Japanese Journal of Applied Physics*, vol. 54, no. 4, p. 040103, 2015.

- [3] M. Barlow, S. Ahmed, A. M. Francis, and H. A. Mantooth, "An integrated sic cmos gate driver for power module integration," *IEEE Transactions* on *Power Electronics*, vol. 34, no. 11, pp. 11191–11198, 2019.

- [4] D. Slater, G. Johnson, L. Lipkin, A. Suvorov, and J. Palmour, "Demonstration of a 6h-sic cmos technology," in 1996 54th Annual Device Research Conference Digest. IEEE, 1996, pp. 162–163.

- [5] J.-S. Chen, K. T. Kornegay, and S.-H. Ryu, "A silicon carbide cmos intelligent gate driver circuit with stable operation over a wide temperature range," *IEEE journal of solid-state circuits*, vol. 34, no. 2, pp. 192–204, 1999.

- [6] D. T. Clark, E. P. Ramsay, A. Murphy, D. A. Smith, R. Thompson, R. Young, J. D. Cormack, C. Zhu, S. Finney, J. Fletcher *et al.*, "High temperature silicon carbide cmos integrated circuits," in *Materials Science Forum*, vol. 679. Trans Tech Publ, 2011, pp. 726–729.

- [7] S. Ahmed, A. U. Rashid, M. M. Hossain, T. Vrotsos, A. M. Francis, and H. A. Mantooth, "Dc modeling and geometry scaling of sic low-voltage mosfets for integrated circuit design," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 7, no. 3, pp. 1574–1583, 2019.

[8] A. Rahman, P. D. Shepherd, S. A. Bhuyan, S. Ahmed, S. K. Akula,

- [8] A. Rahman, P. D. Shepherd, S. A. Bhuyan, S. Ahmed, S. K. Akula, L. Caley, H. A. Mantooth, J. Di, A. M. Francis, and J. A. Holmes, "A family of cmos analog and mixed signal circuits in sic for high temperature electronics," in 2015 IEEE Aerospace Conference. IEEE, 2015, pp. 1–10.

- [9] A. Rahman, K. Addington, M. Barlow, S. Ahmed, H. Mantooth, and A. Francis, "A high temperature comparator in cmos sic," in 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA). IEEE, 2015, pp. 236–240.

- [10] A. Rahman, S. Roy, R. Murphree, H. Mantooth, A. Francis, and J. Holmes, "A sic 8 bit dac at 400° c," in 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA). IEEE, 2015, pp. 241–246.

- [11] A. Rahman, S. Roy, R. Murphree, R. Kotecha, K. Addington, A. Abbasi, H. A. Mantooth, A. M. Francis, J. Holmes, and J. Di, "High-temperature sic cmos comparator and op-amp for protection circuits in voltage regulators and switch-mode converters," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, no. 3, pp. 935–945, 2016.

- [12] A. Rahman, A. M. Francis, S. Ahmed, S. K. Akula, J. Holmes, and A. Mantooth, "High-temperature voltage and current references in silicon carbide cmos," *IEEE Transactions on Electron Devices*, vol. 63, no. 6, pp. 2455–2461, 2016.

- [13] R. C. Murphree, S. Roy, S. Ahmed, M. Barlow, A. Rahman, A. M. Francis, J. Holmes, H. A. Mantooth, and J. Di, "A sic cmos linear voltage regulator for high-temperature applications," *IEEE Transactions on Power Electronics*, vol. 35, no. 1, pp. 913–923, 2019.

- [14] S. Hou, M. Shakir, P.-E. Hellström, B. G. Malm, C.-M. Zetterling, and M. Östling, "A silicon carbide 256 pixel uv image sensor array operating at 400° c," *IEEE Journal of the Electron Devices Society*, vol. 8, pp. 116–121, 2020.

- [15] P. G. Neudeck, D. J. Spry, M. J. Krasowski, N. F. Prokop, and L. Y. Chen, "Demonstration of 4h-sic jfet digital ics across 1000° c temperature range without change to input voltages," in *Materials Science Forum*, vol. 963. Trans Tech Publ, 2019, pp. 813–817.

- [16] N. Yun, J. Lynch, and W. Sung, "Demonstration and analysis of a 600 v, 10 a, 4h-sic lateral single resurf mosfet for power ics applications," Applied Physics Letters, vol. 114, no. 19, p. 192104, 2019.

- [17] S. B. Isukapati, H. Zhang, T. Liu, E. Ashik, B. Lee, A. Morgan, W. Sung, A. Fayed, and A. Agarwal, "Monolithic integration of lateral hv power mosfet with lv cmos for sic power ic technology," in 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD) (accepted). IEEE, 2021.

- [18] D. P. Foty, MOSFET modeling with SPICE: principles and practice. Prentice-Hall, Inc., 1997.

- [19] H.-S. Wong, M. H. White, T. J. Krutsick, and R. V. Booth, "Modeling of transconductance degradation and extraction of threshold voltage in thin oxide mosfet's," *Solid-State Electronics*, vol. 30, no. 9, pp. 953–968, 1087