# Fabrication of Si/GaAs<sub>0.51</sub>Sb<sub>0.49</sub> Heterostructure Diodes via Transfer Printing

Yongkang Xia, Sk Shafaat Saud Nikor, Naga Swetha Nallamothu, Rachel L. Adams, Hyemin Jung, Nathan Gajowski, Seunghyun Lee, Ronald M. Reano, Sanjay Krishna, Steven Ringel, and Shamsul Arafin<sup>\*</sup>

Department of Electrical and Computer Engineering, The Ohio State University, Columbus, OH 43210, USA *Corresponding author: email: <u>arafin.1@osu.edu</u>*

*Abstract*— Si nanomembranes (NMs) with a thickness of 205 nm were grafted onto GaAsSb/InAlAs layers grown on InP via polydimethylsiloxane (PDMS)-stamp-assisted printing. The Si/GaAsSb heterostructure diodes exhibit promising electrical characteristics, paving the path for GaAsSb-Si integrated photodetectors.

Keywords—Transfer printing, wet etching, GaAsSb, photodetector

## I. INTRODUCTION

High-sensitivity avalanche photodiodes (APDs) operating at a wavelength of 1550 nm are important components for telecom applications. Among III-V semiconductors, GaAsSb lattice matched to InP has recently been reported to be an excellent absorber for this particular wavelength [1, 2]. However, due to the lattice mismatch between Si and GaAsSb, it is challenging to directly grow GaAsSb/Si heterostructures [3, 4]. Here, for the first time, we successfully grafted Si nanomembranes (NMs) with sub-micrometer thicknesses onto a GaAsSb/InAlAs/InP heterostructure via transfer printing using a PDMS stamp. As a result, a uniform interfacial contact forms between the transferred NMs and GaAsSb interface by means of van der Waals forces. Electrical characterization were carried out to evaluate the Si-GaAsSb interfaces, with the eventual aim of realizing GaAsSb NM/Si APDs.

## II. EXPERIMENTAL RESULT

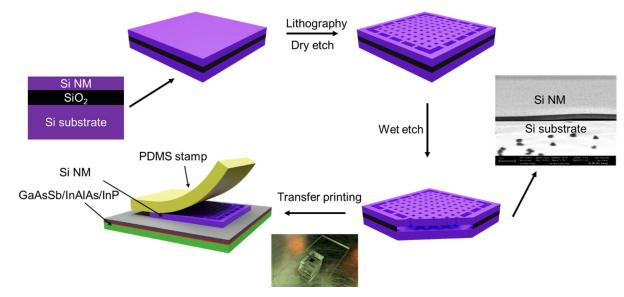

The Si NM transfer printing process is illustrated in Fig. 1. SiO<sub>2</sub> layers in a silicon-on-insulator (SOI) wafer function as a sacrificial layer. Standard photolithography and subsequent dry etching of 205 nm of top Si down to the SiO<sub>2</sub> layer using BCl<sub>3</sub> plasma resulted in the formation of required patterns for the Si NM transfer. The square hole-like patterns were formed in the Si layer, which facilitated the lateral wet etching of SiO<sub>2</sub>. Other patterns on the edge of the NMs, connecting the Si NMs to the external unpatterned Si, serve as anchors to tether the NMs even after the SiO<sub>2</sub> layer underneath is fully removed. Wet etching using 49% HF for 4 hours removed the sacrificial layer, and the Si NM dropped down to the Si substrates as shown by the scanning electron microscope (SEM) image. A PDMS stamp was then utilized to pick up the Si NMs from the original Si substrate and transfer it onto the MBE-grown GaAsSb/AlInAs layers on foreign InP substrates. Van der Waals interactions form a heterostructure diode. The contact between Si and GaAsSb was further enhanced by a subsequent rapid thermal annealing (RTA) at 350°C for 5 minutes in N<sub>2</sub> flow.

Fig. 1 Process flow of Si NM transfer printing on GaAsSb.

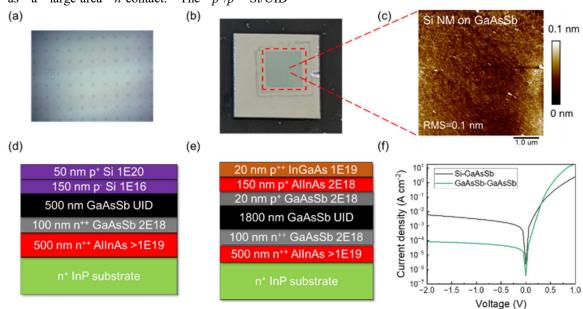

During transfer printing, optimization of the wet etch of the sacrificial layer is critical since it determines the morphology of the Si NM to be printed on GaAsSb. Fig. 2(a) shows a clean Si NM with no obvious residues, obtained after wet etch. To investigate the surface roughness of the Si NM after transfer, shown in Fig. 2(b), atomic force microscopy (AFM) was performed, and a roughness of ~0.1 nm found as shown in Fig. 2(c). The optical microscope and AFM images indicate that the sacrificial layer removal causes negligible damage to the Si NMs. To investigate the carrier transport at the Si/GaAsSb interface and overall electrical performance of the resulting heterostructures in the form of diodes, a Ni/Au metal stack with thicknesses of 10/100 nm was evaporated on the devices. This was followed by RTA at 350°C for 30 seconds under N2 ambient which forms SiNx at the Si/Ni interface. Electrically-conductive solder paste was then used on the backside of the InP substrates, serving as a large-area *n*-contact. The  $p^+/p^-$  Si/UID-

GaAsSb/ $n^{++}$ GaAsSb shown in Fig. 2(d) constitutes a *p-i-n* diode. To analyze the effect of transfer printing on the *p-i-n* diode performance, a homoepitaxially-grown *p-i-n* diode, shown in Fig. 2(e), was used as a reference device. Fig. 2(f) shows the continuous-wave current density-voltage (*J-V*) characteristics of the transfer-printed Si-GaAsSb and the reference GaAsSb-GaAsSb diodes measured at room temperature. Compared to the control diodes, the transfer-printed diode yields a slightly lower forward current density and a far higher reverse current density. Table 1 summarizes the measured electrical parameters. The ideality factor for the transfer-printed diode is ~3, which is larger than that of 1.7 for the control diodes. The higher ideality factor could possibly be attributed to the presence of abundant defects and traps at the Si/GaAsSb interface.

Fig. 2 (a) optical microscope image of Si NM after wet etch; (b) Si NM after transfer onto GaAsSb; (c) AFM image of Si NM on GaAsSb; (d) schematic representation of the Si-GaAsSb structure; (e) schematic representation of the GaAsSb-GaAsSb structure; (f) *J-V* curves of the resulting diodes.

| Table 1: Electrical | parameters | obtained | from | transfer-printe | d and control |

|---------------------|------------|----------|------|-----------------|---------------|

|                     |            | 1 .      |      |                 |               |

| devices.      |                 |                                            |                                 |  |  |  |

|---------------|-----------------|--------------------------------------------|---------------------------------|--|--|--|

| Diode         | Ideality factor | $I_{ m on}/I_{ m off}$ at $\pm 0.8~{ m V}$ | Series                          |  |  |  |

|               |                 |                                            | resistance                      |  |  |  |

| Si-GaAsSb     | 3               | $3.8 \times 10^{2}$                        | $1 \Omega$ -cm <sup>2</sup>     |  |  |  |

| GaAsSb-GaAsSb | 1.7             | $1.5 \times 10^{5}$                        | $0.7 \ \Omega$ -cm <sup>2</sup> |  |  |  |

### **III.** CONCLUSION

Our work reports the transfer printing of Si NM on GaAsSb and the lattice mismatched heterostructure's electrical characterization. Electrical measurements indicate severe nonradiative recombination at the Si/GaAsSb interface. Further outcomes of passivating the interface, optoelectronic measurements, and attempts to transfer GaAsSb NM on Si will be presented at the conference.

#### ACKNOWLEDGMENT

The authors acknowledge support by the Intel<sup>®</sup> Semiconductor Education and Research Program for Ohio.

#### REFERENCES

[1] S. Lee et al., "High gain, low noise 1550 nm GaAsSb/AlGaAsSb avalanche photodiodes," Optica, vol. 10, no. 2, 2023, doi: 10.1364/optica.476963.

[2] H. Jung, S. Lee, Y. Liu, X. Jin, J. P. R. David, and S. Krishna, "High electric field characteristics of GaAsSb photodiodes on InP substrates," Applied Physics Letters, vol. 122, no. 22, 2023, doi: 10.1063/5.0154844.

[3] J. Justice, C. Bower, M. Meitl, M. B. Mooney, M. A. Gubbins, and B. Corbett, "Wafer-scale integration of group III–V lasers on silicon using transfer printing of epitaxial layers," Nature Photonics, vol. 6, no. 9, pp. 610-614, 2012, doi: 10.1038/nphoton.2012.204.

[4] B. Corbett, R. Loi, W. Zhou, D. Liu, and Z. Ma, "Transfer print techniques for heterogeneous integration of photonic components," Progress in Quantum Electronics, vol. 52, pp. 1-17, 2017, doi: 10.1016/j.pquantelec.2017.01.001.